IBM passe au 22 nm pour ses prochains processeurs et circuits mémoires destinés aux serveurs.

San Francisco – IBM a présenté lors de la conférence ISSCC les deux circuits qui orchestrent sa prochaine génération de serveurs System z.

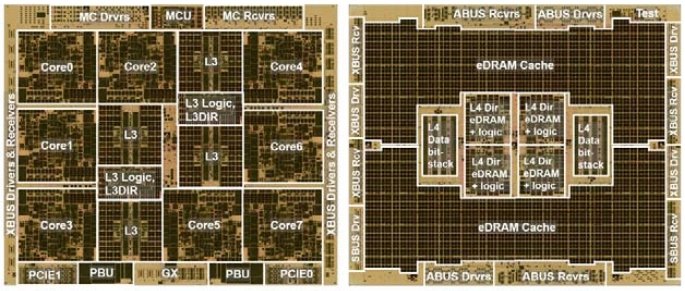

Le premier est un microprocesseur à huit coeurs, versions améliorées de l’actuel zEC12 et capables de traiter chacun six instructions Cisc par cycle d’horloge en les décomposant en plusieurs micro-instructions Risc. Les 64Mo de DRam embarquée sont utilisés non seulement comme cache de niveau 3, mais aussi au niveau 2, au plus près des coeurs.

Une interface spécifique permet à cette puce de se connecter à deux autres processeurs identiques et à la mémoire cache de niveau 4 contenue dans le second circuit présenté par IBM. Ce dernier comprend 480Mo de DRam embarquée et tourne à une fréquence réduite de moitié par rapport au processeur (lequel monte jusqu’à 5,2GHz).

Les deux circuits sont fabriqués en Cmos 22nm sur SOI, là où la précédente génération utilisait le 32 nm.