Ce circuit FinFET à deux ports PHY Ethernet 400 Gbit/s vise les centres de données, les réseaux d’entreprise et les infrastructures 5G.

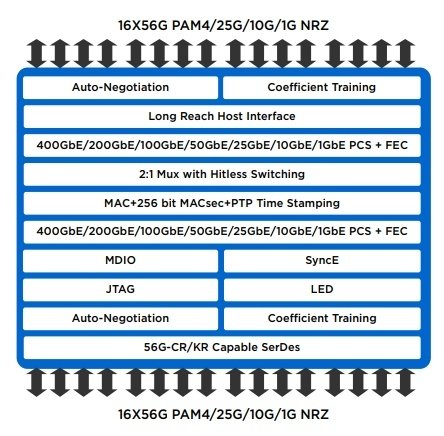

Marvell embarque sur une puce deux blocs d’émission-réception PHY Ethernet 400 Gbit/s avec cryptage IEEE802.1AE 256 bits et synchronisation PTP classe C. Ce circuit référencé 88X7121P trouvera notamment sa place dans les centres de données et les infrastructures 5G. Actuellement en cours d’échantillonnage, il est basé sur la technologie de mise en série-parallèle (Serdes) 56G PAM4 du fabricant, et peut être paramétré pour gérer deux ports à 400Gbit/s, quatre ports à 200Gbit/s, huit ports à 100Gbit/s ou 16 ports à 50Gbit/s.