L’Imec et le centre Holst ont présenté un circuit adaptant la fréquence d’échantillonnage aux aléas du rythme cardiaque, réduisant la consommation de l’ensemble de la chaine de traitement du signal. San Francisco – L’institut belge de R&D en microélectronique Imec et le Centre Holst ont profité de la conférence ISSCC, qui vient d’ouvrir ses portes à San Francisco, pour présenter un circuit frontal analogique qui permettrait de réduire d’un facteur 5 la consommation d’un implant de surveillance cardiaque. Ce circuit spécifique tire parti d’un algorithme d’échantillonnage adaptatif réduisant la charge de travail du DSP et de l’émetteur RF associés. Embarquant des canaux de lecture en quadrature et un convertisseur analogique-numérique, il utilise en effet une technologie de détection d’activité qui adapte la fréquence d’échantillonnage du CAN en fonction des variations du rythme cardiaque. Il ne consomme que 20 µW sous 2 V, le système cardiaque complet ne nécessitant que 300 µW.

Dans la même rubrique

Le 07/01/2022 à 11:01 par Christelle Erémian

Les ventes mondiales de semi-conducteurs devraient atteindre 680Md$ en 2022

D’après le cabinet d’études IC Insights, les ventes de semi-conducteurs devraient augmenter de 11% en 2022 pour atteindre 680,6Md$. Un…

Le 04/11/2021 à 10:29 par Christelle Erémian

Les livraisons de semi-conducteurs atteignent des records au troisième trimestre 2021

Alors que la pénurie de composants perdure, jamais autant de puces n'auront été livrées au cours de l'histoire du marché…

Le 13/09/2021 à 8:46 par Frédéric Rémond

Pluie de microcontrôleurs Cortex-M4 200MHz chez Toshiba

Le Japonais étoffe sa gamme TXZ+ de microcontrôleurs 32 bits haut de gamme d'une vingtaine de modèles. Toshiba ajoute vingt…

Le 13/09/2021 à 8:23 par Frédéric Rémond

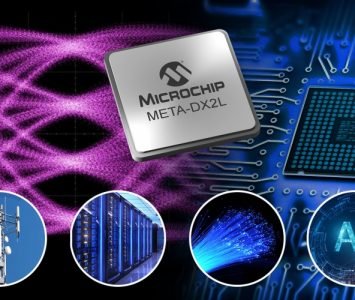

Les circuits Ethernet PHY adoptent les ports à 112Gbit/s

Microchip développe un circuit Ethernet PHY compact, à faible consommation et gérant jusqu'à 1,6Tbit/s. L'explosion des débits de…