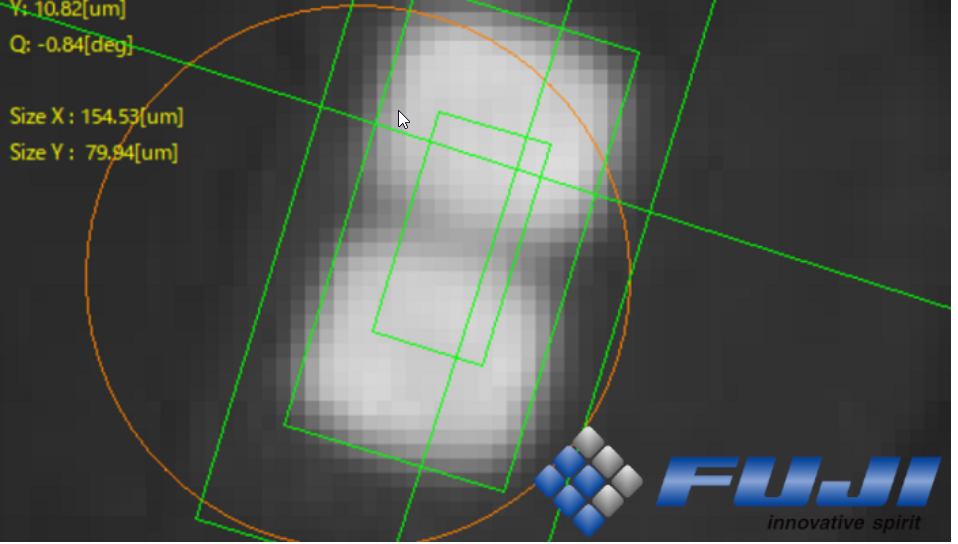

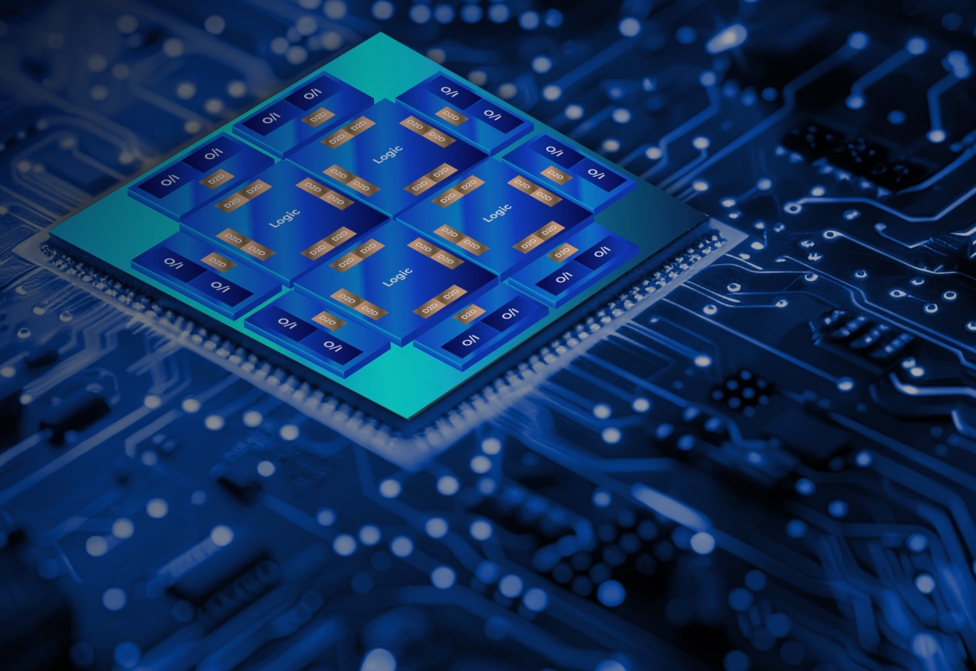

Des chiplets UCIe d’interconnexion puce-à-puce véhiculant 64Gbit/s ? C’est ce que propose la troisième génération de sous-systèmes IP d’Alphawave Semi, une première selon l’Anglais qui culminait jusqu’ici à 36Gbit/s avec sa Gen2. Disponibles dans le process 3nm du fondeur taïwanais TSMC, ces chiplets peuvent être configurés en fonction de différents protocoles comme AXI-4, AXI-S, CXS, CHI et CHI-C2C. Ils permettent d’augmenter la bande passante entre mémoires et processeurs au sein des centres de données, avec une densité dépassant théoriquement les 20Tbit/s par millimètre.

Des chiplets UCIe d’interconnexion à 64 Gbit/s !

© Alphawave