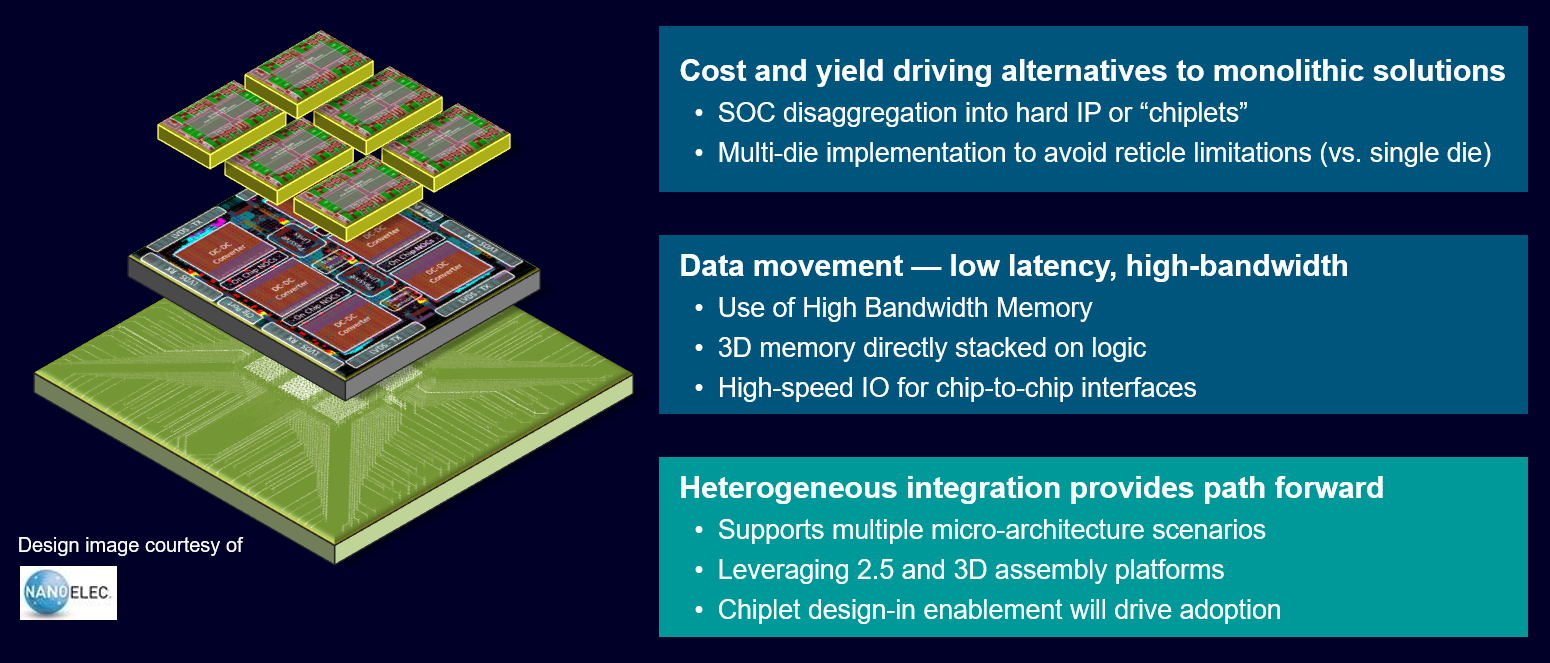

Aujourd’hui, tenir la cadence définie par la loi de Moore reste un défi et incite à adopter des techniques d’encapsulation innovantes qui permettent une mise à l’échelle continue des systèmes pour un coût inférieur à celui des dispositifs monolithiques comparables.

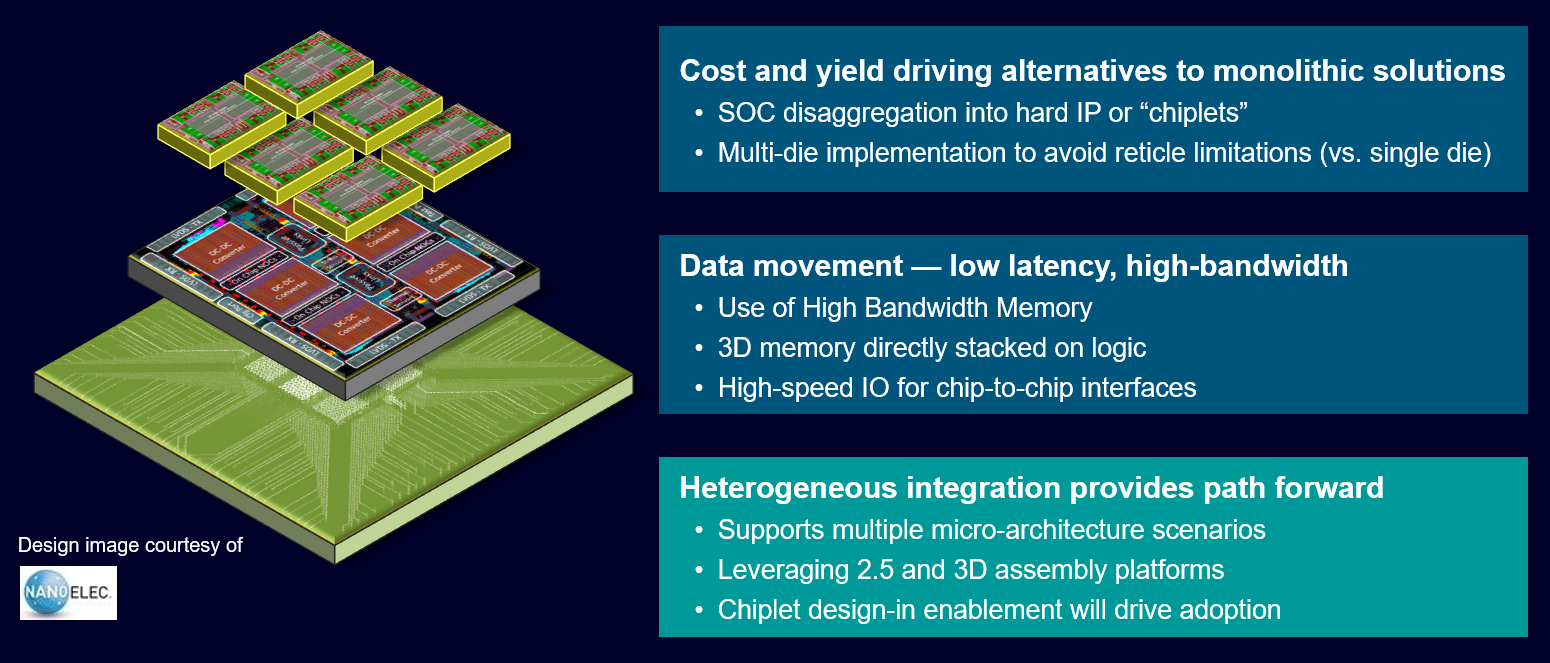

Figure 1. Les chiplets permettent de résoudre les problèmes de mise à l’échelle des systèmes à semi-conducteurs.

Ces techniques d’encapsulation divisent ce qui serait généralement un dispositif homogène et monolithique, tel qu’un ASIC ou un SoC, en puces discrètes sans boîtier, appelées chiplets , spécialement conçues et optimisées pour fonctionner avec d’autres chiplets à l’intérieur d’un même boîtier. Ce procédé, également appelé intégration hétérogène (ou HI, pour heterogeneous integration ) consiste à intégrer plusieurs puces ou chiplets dans une conception de type boîtier-système (ou SiP, pour system in package ).

Les SiP à intégration hétérogène offrent des avantages considérables : performances supérieures, consommation d’énergie réduite, surface plus faible, coût moindre et mise sur le marché plus rapide. Cependant, à ce jour, seul un petit nombre d’entreprises de pointe sont capables d’en concevoir et d’en produire. Leur large diffusion dans l’industrie nécessitera de normaliser les modèles de chiplets et l’IP de connectivité entre puces, un processus qui est en cours, et d’adopter de nouveaux flux de travail.

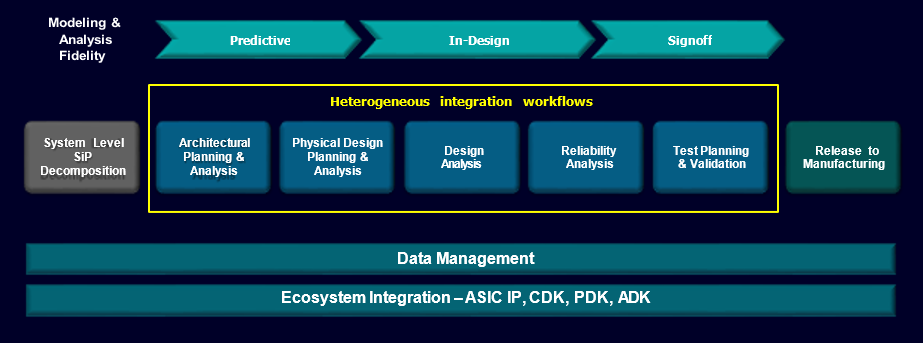

Dans cet article, nous allons nous concentrer sur cinq flux de travail essentiels à la planification, à la coconception, à la mise en œuvre et à la vérification des conceptions hétérogènes.

- Planification et analyse architecturales

- Planification et analyse de la conception physique

- Analyse de la conception

- Analyse de la fiabilité

- Planification et validation des tests

Figure 2. Flux de travail d’intégration hétérogène.

À mesure qu’une conception progresse dans ces cinq flux de travail, elle est également modélisée et analysée afin de vérifier en permanence qu’elle répond aux spécifications de performance.

La modélisation prédictive est effectuée lors des étapes de planification de l’architecture et de la conception physique, avec pour objectif principal de valider les décisions d’ingénierie et de connaître les performances en aval. Cela permet également aux membres de l’équipe de s’assurer qu’ils choisissent l’architecture système et le boîtier les mieux adaptés aux problèmes à résoudre.

La modélisation en cours de conception permet de valider davantage une conception à mesure que des contenus et détails nouveaux deviennent disponibles pendant la mise en œuvre. L’objectif est d’identifier et de résoudre les problèmes tant que les mesures correctives sont encore relativement simples et peu coûteuses. Ces problèmes sont généralement liés à l’alimentation, à la température, à l’intégrité du signal, aux règles de processus, voire à l’intégration mécanique.

La dernière étape consiste à approuver définitivement la conception finale avant sa mise en production. Comme les conceptions HI comportent un large éventail de propriété intellectuelle et de contenus de conception multidomaines, une gestion complète des données est nécessaire tout au long des cinq flux de travail.

Étudions maintenant ces cinq flux de travail plus en détail.

Planification et analyse architecturales

Le flux de travail de planification et d’analyse architecturales permet aux concepteurs de systèmes et de RTL d’étudier et capturer rapidement des architectures de conception viables en s’appuyant sur trois éléments-clés :

- les composants de type chiplet et les kits de conception correspondants,

- les protocoles à haut débit standards pour les interfaces internes entre puces au sein du boîtier,

- les interfaces externes de puce à puce entre le boîtier du SiP et d’autres puces au sein du système au niveau du PCB.

Ces interfaces à haut débit peuvent être capturées à l’aide d’une bibliothèque de modèles d’IP de connectivité génériques, puis mappées sur d’autres IP de connectivité propres à un fournisseur et à une technologie. Cela permet au concepteur du système d’évaluer les caractéristiques d’alimentation, de performances, de surface et de coût de différents scénarios par rapport au cahier des charges du système.

La modélisation prédictive aide ainsi les ingénieurs à se concentrer sur la microarchitecture optimale en identifiant un ensemble fini de scénarios, ou microarchitectures, et en étudiant plusieurs scénarios de configuration et de partitionnement.

Planification et analyse de la conception physique

Une fois déterminée l’architecture optimale du SiP, la conception détaillée peut commencer ; elle inclut la planification physique, la mise en œuvre et l’analyse.

Le processus de planification et d’analyse de la conception physique concerne les interposeurs et les substrats des boîtiers. Il englobe la définition du plan de masse du boîtier, la planification des E/S, l’alimentation électrique, la faisabilité du routage des substrats et l’optimisation de la netlist (liste d’interconnexions), ainsi que les vérifications correspondantes, telles que LVS et LEC.

La modélisation prédictive est utilisée lors de la définition du plan de masse et de la mise en œuvre afin de vérifier en permanence la conception, ce qui permet de rationaliser le processus de conception. À mesure que des structures de conception détaillées, telles que les plans d’alimentation, sont mises en œuvre, la fidélité de la modélisation et la qualité des résultats s’améliorent.

La coconception d’un ou plusieurs chiplets personnalisés étant fondamentale, il est essentiel de garantir une collaboration étroite entre les équipes de conception des puces et du boîtier. Cela implique la mise en place d’une gestion robuste des données de conception multidomaine et une prise en charge complète des ordres de modification technique afin de faciliter l’échange de données entre les équipes et les disciplines.

Analyse de la conception

Le flux de travail d’analyse de la conception inclut des outils d’extraction et de simulation qui prennent en charge l’analyse de l’intégrité du signal et de l’alimentation du SiP, la chute de tension IR statique et dynamique, l’électromigration et la synchronisation.

Les techniques traditionnelles d’analyse de l’intégrité du signal peuvent être utilisées pour simuler les interfaces à haut débit. Une analyse de synchronisation statique est nécessaire pour les signaux à faible débit et les connexions de test et de contrôle.

L’approche d’analyse de l’intégrité de l’alimentation doit être adaptée pour tenir compte des scénarios multichiplets. En effet, ces structures nécessitent une extraction détaillée des parasites qui prend en charge à la fois les substrats en silicium et les substrats organiques, ainsi qu’une extraction combinée au niveau du SiP et de la puce pour l’analyse de la chute de tension IR et de l’électromigration.

Analyse de la fiabilité

Les contraintes thermiques et mécaniques sont deux domaines-clés qui nécessitent une analyse approfondie de la fiabilité. Compte tenu de la proximité des composants dans les conceptions HI, il existe un risque élevé d’interaction entre les puces ou entre les puces et le boîtier. Le couplage thermique peut donc poser un problème majeur.

Ce niveau d’analyse intensif nécessite des modèles thermiques détaillés des puces. Ces modèles doivent tenir compte de la densité de puissance et de l’échauffement des transistors au niveau de la puce, et il n’est plus réaliste de supposer une température uniforme sur toute la puce.

Les contraintes mécaniques peuvent également poser problème en raison de la taille du substrat et des différents matériaux utilisés. Par exemple, dans le cas d’un interposeur en silicium de grande taille comportant plusieurs réticules posé sur un substrat de boîtier organique, l’analyse doit tenir compte des différents coefficients de dilatation thermique et évaluer des effets tels que les contraintes dues aux bosses ou au gauchissement du substrat induits par cette dilatation.

Tant au niveau des puces qu’au niveau des SiP, il convient également de réaliser la conception en tenant compte de la fabrication ( design for manufacturing ) et de vérifier le respect des règles électriques. Il s’agit notamment de vérifier les éventuels problèmes d’électromigration, de décharges électrostatiques, de verrouillage à l’état passant et de contraintes électriques excessives. Pour accélérer ce type d’analyse des SiP, les données de performance et les modèles de chiplets requis doivent être inclus dans leurs kits de conception respectifs.

Planification et validation des tests

En matière d’intégration hétérogène, les tests de fabrication constituent sans doute l’un des processus les plus complexes, car ils nécessitent une infrastructure DFT ( design for testing , conception en vue des tests), un test au niveau de la plaquette, un test des puces dans le boîtier et un test de l’interface entre les puces.

La bonne nouvelle, c’est qu’il existe des normes DFT pour tester les conceptions 2,5D et 3D ; il s’agit des normes IEEE 1838, 1687 et 1149.1. De plus, ce processus est pris en charge par les récentes avancées en matière de DFT, telles que les tests de mémoire et les autotests intégrés (MBIST) avec des ports de test conformes à la norme 1838 ; les tests de balayage, qui prennent en charge un flux de reciblage des vecteurs de test de boîtiers 3D ; et les tests d’interconnexion entre puces, qui utilisent des chaînes de schémas d’usure différentielle (DWR) composées de cellules wrapper . Il est essentiel que ces méthodes soient intégrées dès le début pour qu’il soit possible de tester les SiP ; cela nécessite de planifier l’accès aux plots de test et les E/S de test au niveau du boîtier, des exigences de planification qui sont similaires à celles concernant les E/S à haut débit.

De même, il est impératif de comprendre que les considérations relatives aux tests ne peuvent attendre la fin de l’étape de conception et qu’elles doivent également être intégrées dès les premiers stades de la planification. Les ingénieurs spécialistes des boîtiers doivent collaborer avec les ingénieurs de test pour élaborer le plan des E/S de test et tenir compte des exigences en matière d’analyse de synchronisation statique et de simulation de synchronisation.

La coconception multidomaine permet de bénéficier des avantages de l’intégration hétérogène

Pour réussir à créer des systèmes hétérogènes intégrés, il convient d’utiliser des flux de travail multidomaines intégrés et des méthodes de conception collaborative tout au long du cycle de conception.

La conception hétérogène génère une quantité considérable de données multidomaines couvrant l’ensemble du cycle de vie du produit. Cela impose de gérer une base de données de conception pour le système, le RTL, le silicium et même la conception mécanique. La conception HI fait également appel à un large éventail de propriété intellectuelle, de matériaux et de kits de conception. Toutes ces données doivent être soigneusement gérées et synchronisées afin de garantir l’efficience et l’intégrité de la conception tout au long du processus.

L’intégration hétérogène présente de nombreux avantages. Elle permet de créer des systèmes plus grands et plus complexes que les SoC monolithiques et d’améliorer la puissance, les performances, la surface et les facteurs de forme. Cependant, ces avantages ont un coût. Il existe des défis majeurs à relever, tels que la décomposition optimale et le choix de l’architecture, l’alimentation électrique du système, ainsi que la gestion thermique, la synchronisation et les tests. Les entreprises qui souhaitent relever ces défis avec succès et tirer pleinement parti des avantages de la conception HI doivent concentrer leurs efforts sur la création, la qualification et le déploiement des cinq flux de travail présentés dans cet article.

Pour en savoir

plus : EDA Software, Hardware & Tools | Siemens Software

Auteurs

Kevin Rinebold est directeur technique chargé des solutions d’encapsulation hétérogène chez Siemens EDA. Professionnel du marketing des hautes technologies, il possède 24 ans d’expérience dans la direction de gammes de produits et le développement commercial, ainsi qu’une solide expérience en conception électronique. Communicateur efficace, son style de gestion collaboratif et entrepreneurial se traduit par une exécution cohérente des plans d’affaires et la livraison de produits de pointe. C’est avec passion qu’il collabore avec les clients afin de leur fournir des solutions innovantes tout en identifiant de nouvelles opportunités commerciales pour augmenter la valeur des gammes de produits et booster la croissance.

Todd Burkholder est rédacteur et réviseur senior chez Siemens DISW. Depuis 1997, il travaille avec des PME et des clients pour créer du contenu pour la plupart des divisions de Mentor Graphics et de Siemens spécialisées dans l’EDA. Il a débuté sa carrière dans le marketing des hautes technologies en 1992, après avoir obtenu une licence en sciences à l’université d’État de Portland et une maîtrise de lettres à l’université de l’Arizona.