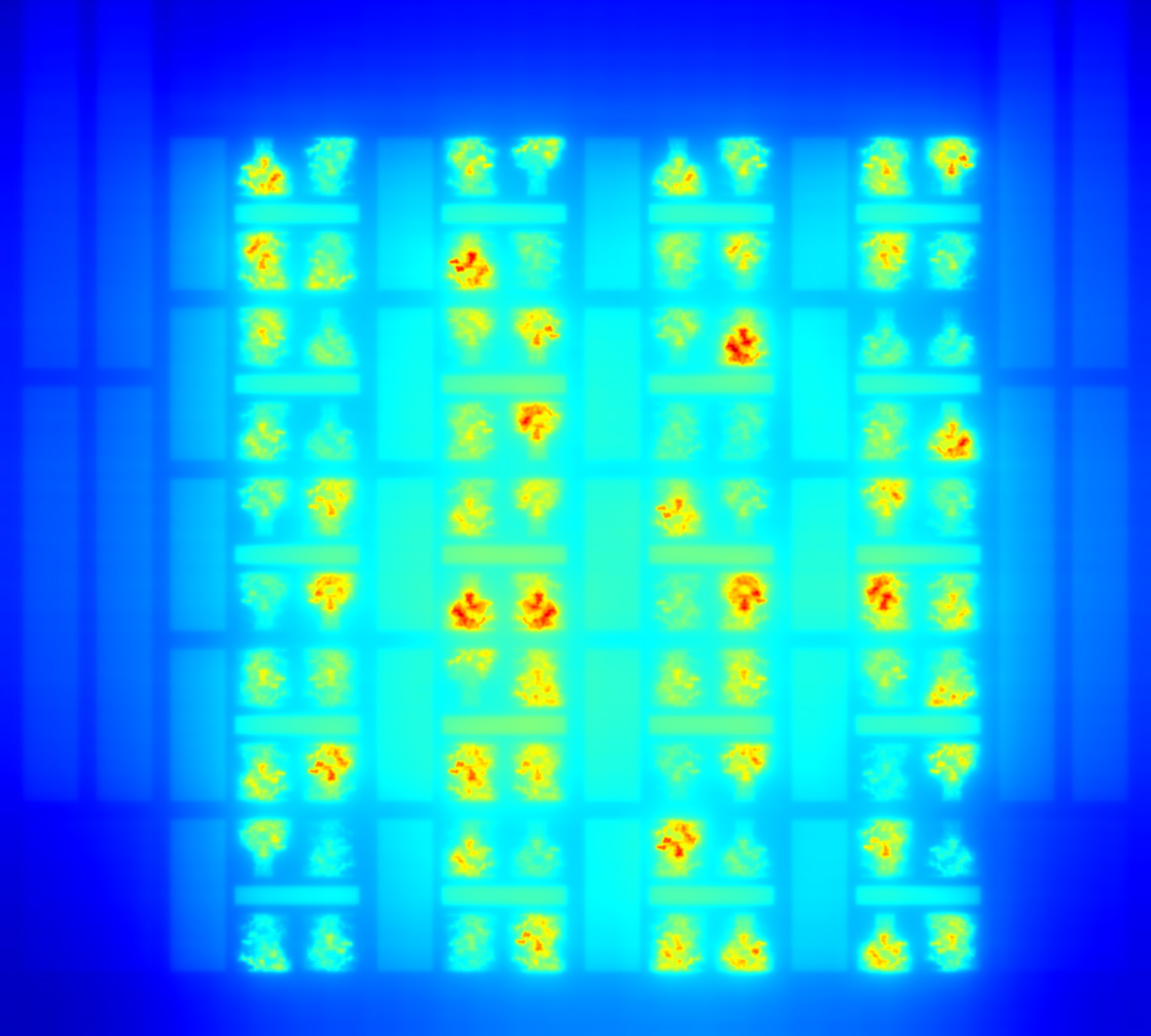

Lors de la conférence IEDM qui se déroule actuellement à San Francisco, l’imec a présenté une étude thermique complète de l’intégration de mémoires HBM sur processeur graphique basée sur la co-optimisation système-process. Cette étude identifie les points chauds d’un tel assemblage dans les architectures de calcul IA ; elle apporte également des solutions permettant selon le centre de R&D belge de réduire la température crête du GPU de 140,7 à 70,8°C.

Dans le modèle étudié, quatre mémoires HBM (contenant chacune douze puces Dram empilées) sont placées directement sur le processeur graphique au moyen de microbumps. Par rapport à l’agencement actuel dans lequel les mémoires HBM entourent le GPU, l’accès plus direct aux mémoires compense ici largement la baisse de fréquence du GPU nécessaire pour maintenir sa température dans des limites acceptables. L’imec étudie également des configurations où le GPU est positionné au-dessus des mémoires.