Pour son bloc d’IP USB SuperSpeed 3.0, Synopsys met à disposition des développeurs un des premiers modèles au niveau système de cette interface, conforme aux spécifications TLM 2.0 de l’OSCI. Face aux besoins de développer du logiciel embarqué le plus tôt possible dans le cycle de conception d’un SoC, Synopsys propose pour ses blocs d’IP USB SuperSpeed3.0 des modèles de haut niveau qui supportent les spécification de l’API TLM 2.0 (Transaction Level Models) décrite par l’Open SystemC Initative (OSCI). Écrits en SystemC, ces modèles sont notamment utilisables au sein de plateformes virtuelles qui autorisent l’écriture et le débogage de piles logicielles bien avant que le code RTL, et à fortiori les premiers prototypes matériels, soient disponibles.Ces modèles TLM, qui sont des représentations au niveau transactions de l’IP de l’interface USB 3.0 elle même et de l’IP du contrôleur Host xHCI (qui font partie de la bibliothèque DesignWare de Synopsys), fonctionnent sous n’importe quel simulateur SystemC conforme à la norme IEEE1666.

Dans la même rubrique

Lecture offerte

Le

13/02/2026

à

7:10

par

Frédéric Rémond

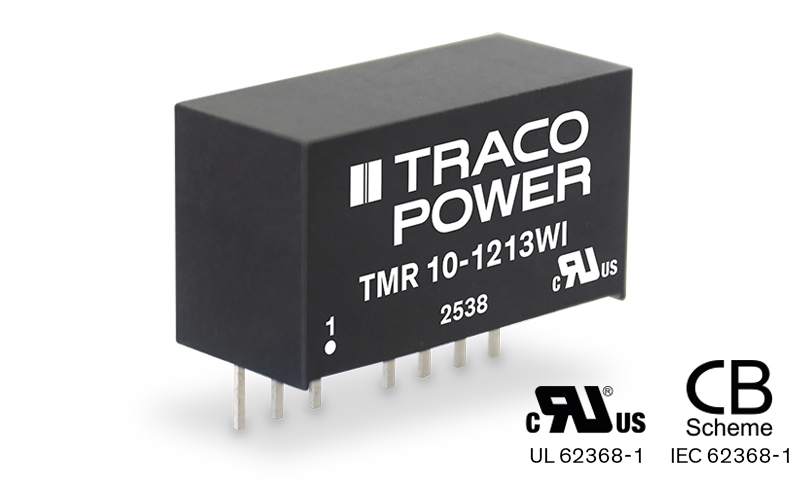

10 W de conversion DC-DC dans un boîtier SIP 8

C'est principalement aux applications industrielles que Traco Power destine ses TMR 10WI, des convertisseurs DC-DC isolés gérant 10W dans un…

Lecture offerte

Le

10/02/2026

à

7:15

par

Frédéric Rémond

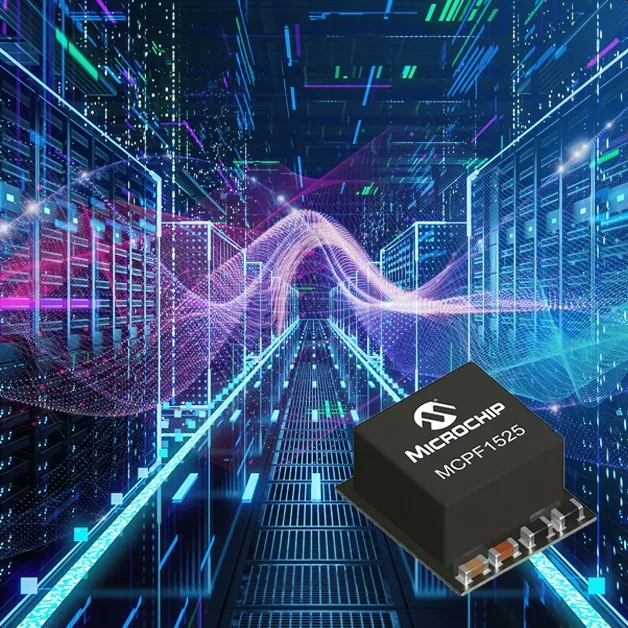

25 A dans un module DC-DC miniature

Les équipements d'intelligence artificielle s'appuient sur des processeurs et des commutateurs PCIe qui ont besoin de composants d'alimentation performants, mais…

Lecture offerte

Le

05/02/2026

à

7:23

par

Frédéric Rémond

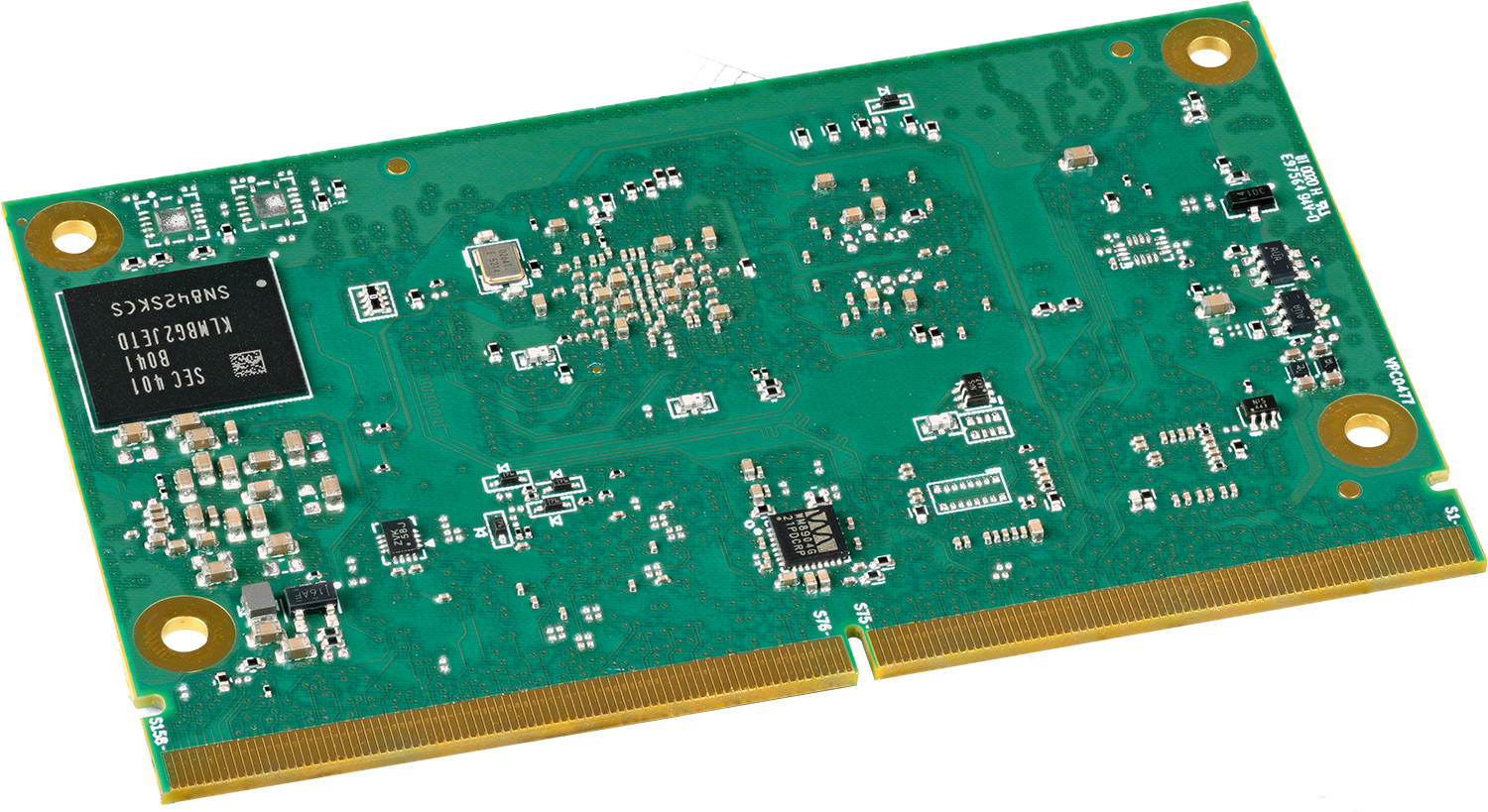

Variscite se met aux modules Smarc

L'Israélien Variscite vient de lancer sa première famille de modules au format Smarc, dont le premier modèle s'appuie sur le…

Lecture offerte

Le

04/02/2026

à

7:17

par

Frédéric Rémond

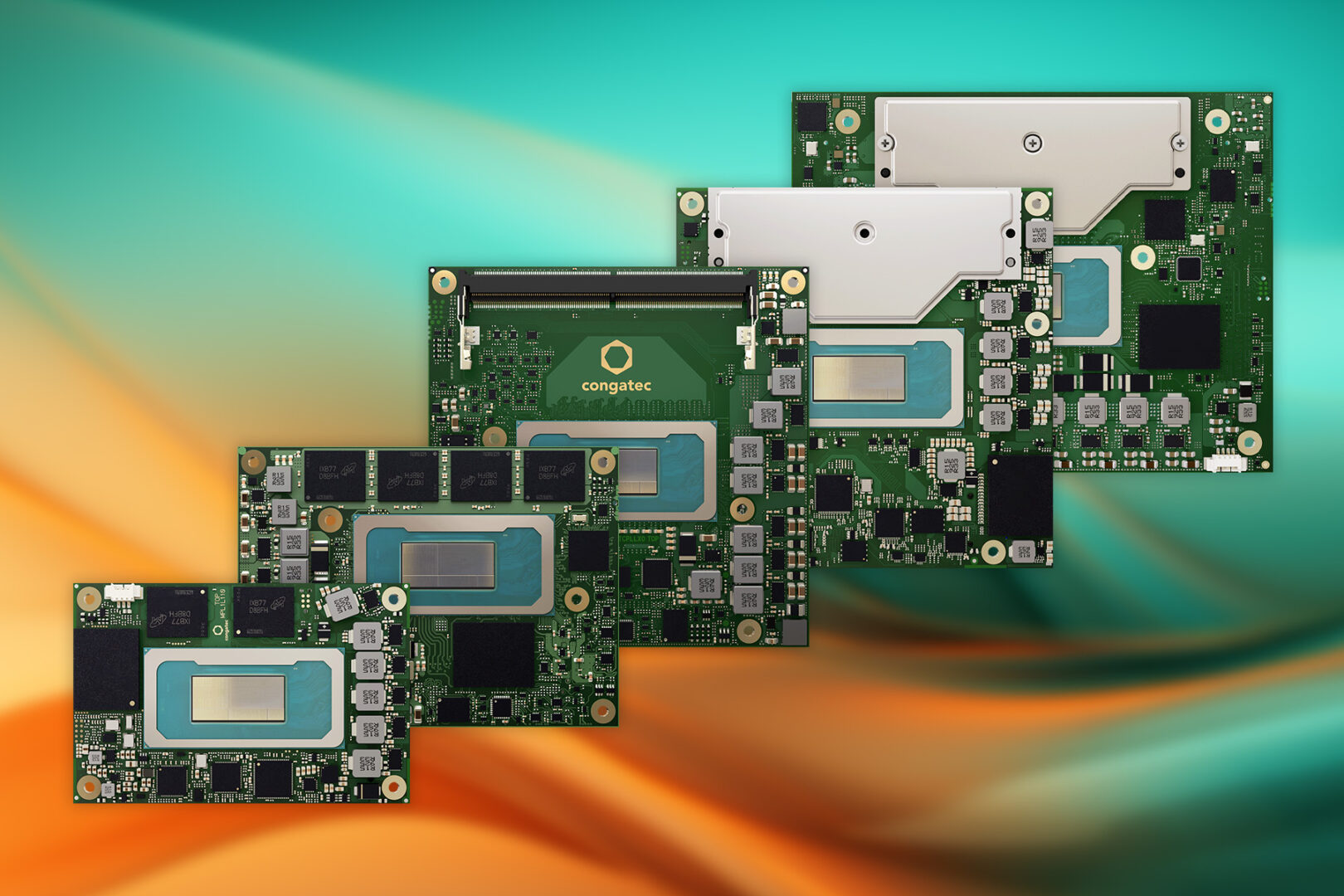

Pluie de modules à processeurs Panther Lake

Dans la foulée de la présentation des processeurs Panther Lake (Core Ultra 3) d'Intel au dernier CES de Las Vegas,…