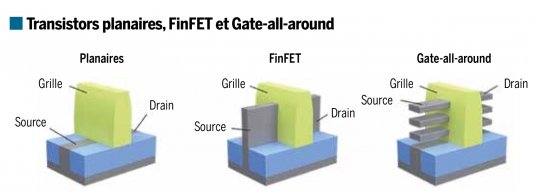

L’AMÉRICAIN EST LE PREMIER À FAIRE LA DEMONSTRATION DE CIRCUITS INTÉGRÉS GRAVES EN PROCESS 2 nm, GRÂCE À UNE TECHNOLOGIE À NANOFEUILLES PLUS PERFORMANTE, ET MINIATURISABLE, QUE LES TRANSISTORS FINFET ACTUELS. À mesure que les géométries se réduisent et donc que les électrons se font rares, les grilles tendent à enserrer le plus possible le…

La lecture de cet article est réservée aux abonnés.

Connectez-vous ou abonnez-vous pour y accéder.