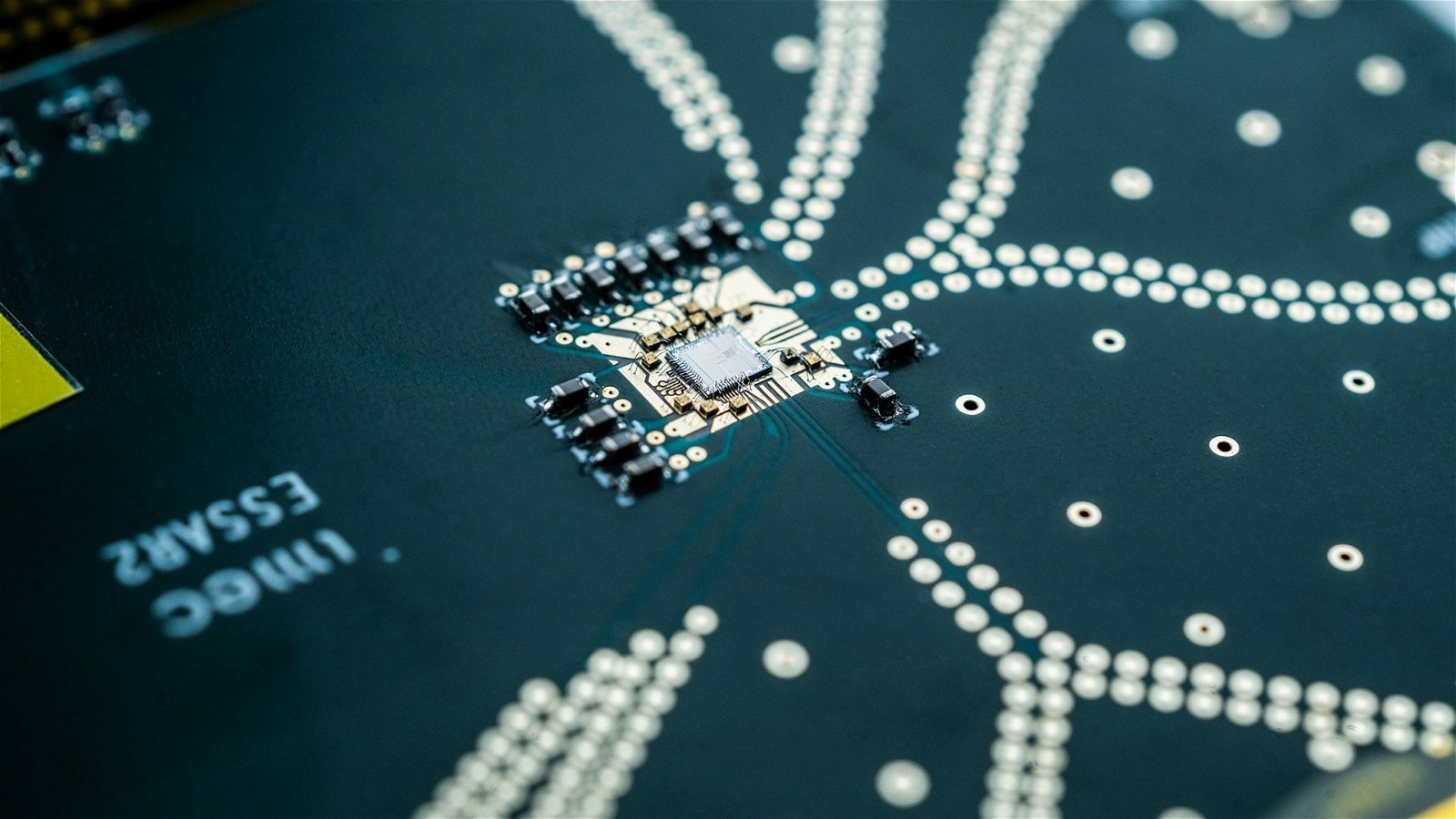

L’Imec a présenté, dans le cadre de la conférence ISSCC de San Francisco, une nouvelle architecture de conversion analogique-numérique convenant entre autres aux liaisons filaires à très haut débit, par exemple au niveau des émetteurs-récepteurs optiques des centres de données. Le centre de R&D belge assure avoir dépassé les limites des CAN à approximations successives (SAR), qui deviennent encombrants pour des communications dépassant les 100Géch/s. Il a présenté un prototype de convertisseur 7 bits 42Géch/s fabriqué en process FinFET 16nm et basé sur une architecture dite massively time-interleaved slope. Combinant en fait un réseau de 768 convertisseurs à pente, la puce n’occupe que 0,07mm², deux fois moins que les approches alternatives selon l’Imec, et ne consomme que 96mW. « C’est la première preuve que notre architecture fonctionne, et ses bénéfices deviendront de plus en plus significatifs à mesure que les fréquences augmentent », assure Joris Van Driessche, responsable de ce programme à l’Imec. Une version 5nm visant les 150Géch/s est en cours d’achèvement, et l’équipe étudie l’implémentation en 2nm en espérant dépasser les 250Géch/s.

Une nouvelle architecture pour les CAN à très haut débit !