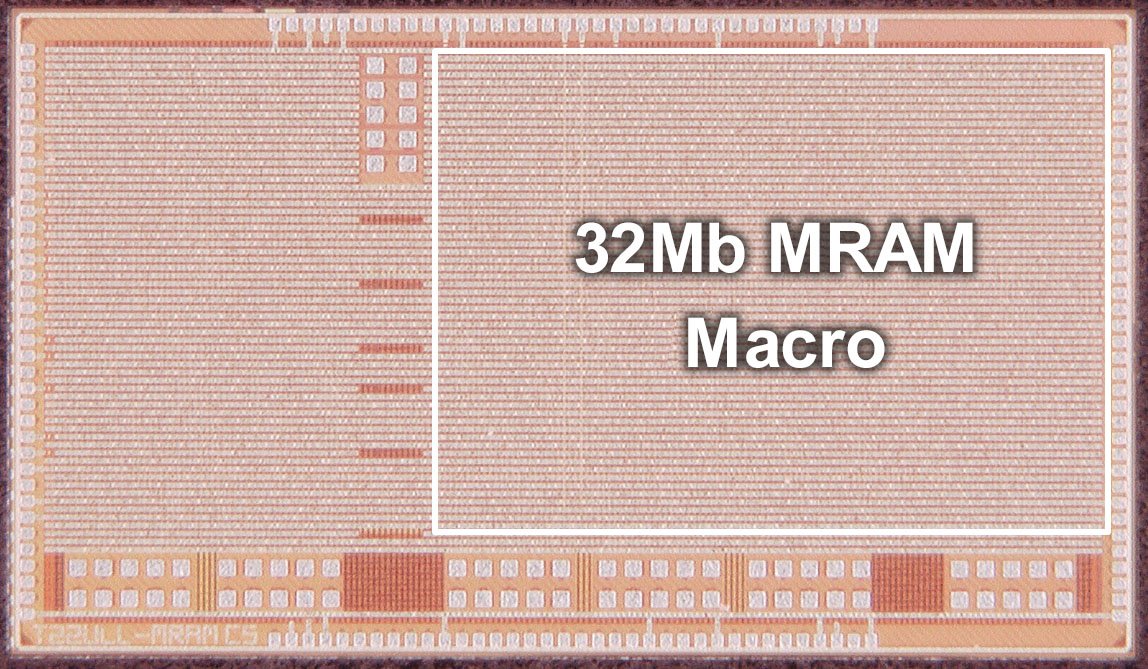

Renesas Electronics a profité de l’édition 2022 du récent Symposium on VLSI Technology and Circuits organisé par l’IEEE pour présenter une technologie de mémoire STT-Mram en process 22nm. Le circuit test comprend 32Mbits de mémoire magnétorésistive avec un temps d’accès en lecture aléatoire de 5,9ns seulement et un débit de données de 5,8Mo/s en écriture. Ces travaux visent à remplacer la mémoire flash au sein des microcontrôleurs, en travaillant principalement sur la rapidité de la Mram. Ici, le Japonais a par exemple réussi à n’alimenter que les zones de mémoire pertinentes en fonction de leur adresse, afin de réduire la charge capacitive parasite dans cette zone et, in fine, de réduire de 30% environ le temps d’écriture. En lecture, le fabricant a agi sur l’amplificateur différentiel utilisé pour distinguer la différence de tension correspondant au niveau logique de chaque cellule. In fine, Renesas espère que ces avancées permettront de produire des microcontrôleurs embarquant une Mram cadencée à plus de 100MHz.

Des progrès significatifs pour la mémoire STT-Mram de Renesas