L’organisme de normalisation Accelera vient de publier un document décrivant l’ensemble des bonnes pratiques de développement de blocs d’IP de vérification (VIP, Verification Intellectual Property). L’objectif: améliorer l’interopérabilité entre les différentes méthodes de test utilisées sur le terrain et une meilleure réutilisation des blocs d’IP de vérification. Le guide détaille ainsi comment utiliser des composants VIP développés en System Verilog et basés sur les méthodologies OVM (Open Verification Methodology) ou VMM (verification Methdology Manual). On y trouve notamment des librairies de références, utilisables dans les deux méthodologies, et des règles de développement d’environnements de vérification, interopérables, au niveau système.

Dans la même rubrique

Le 19/04/2024 à 9:00 par Arnaud Pavlik

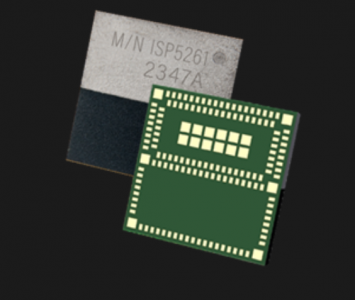

Insight SiP lance un module combo Bluetooth LE / Wi-Fi 6 miniature

Au cours du salon Embedded World 2024 qui a fermé ses portes le 11 avril, le développeur de modules radiofréquences…

Le 19/04/2024 à 8:31 par Frédéric Rémond

Teledyne FLIR propose un module miniature pour ses algorithmes de vision Prism AI

Teledyne FLIR, la filiale de Teledyne dévolue à l'imagerie (notamment thermique), a opté pour le processeur QCS8550 de Qualcomm dans…

Le 15/04/2024 à 8:22 par Frédéric Rémond

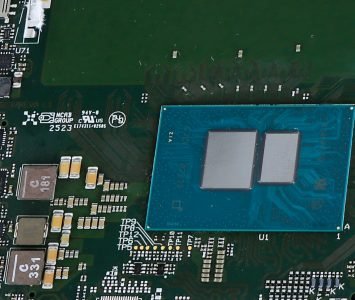

Seco met du Amston Lake dans ses modules COM Express

Présenté pour la première fois lors du salon Embedded World qui vient de fermer ses portes à Nuremberg, le module…

Le 04/04/2024 à 9:00 par Frédéric Rémond

Convertisseurs de puissance : l’Autrichien Recom s’étend en Thaïlande

Le fabricant autrichien de modules de puissance Recom vient d'ouvrir un nouveau centre de fabrication, de distribution et de service…