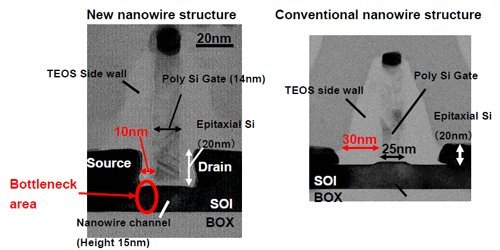

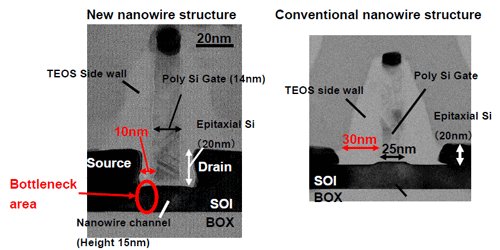

En améliorant son transistor de type nanowire, Toshiba a réduit la résistance parasite et augmenté de 75 % le niveau de courant à l’état passant (1 mA/µm). L’objectif est de réduire les fuites de courant devenues rédhibitoires avec les structures planaires traditionnelles. Ces travaux seront présentés le 17 juin à Hawaï lors du symposium VLSI Technology.