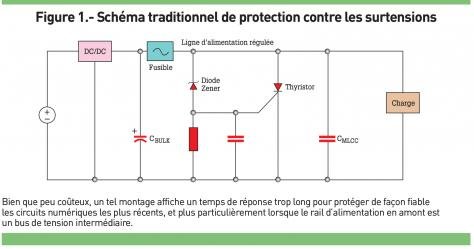

La demande du marché pour des systèmes plus performants offrant une disponibilité accrue, couplée avec le coût important des derniers processeurs numériques, imposent la mise en œuvre de stratégies de réduction des risques, notamment lors de l’apparition de surtensions transitoires sur un rail d’alimentation.

L es tensions de bus intermédiaire de 24V ~ 28V en

…